引子:

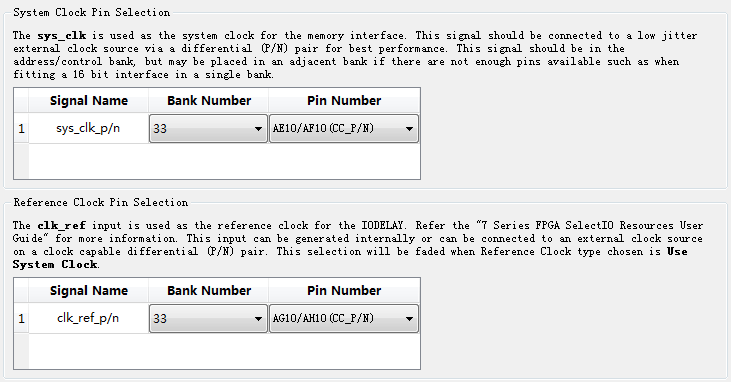

HP中的DDR需要sys_clk和clk_ref两路输入,HR用户功能也需要usr_clk时钟输入。

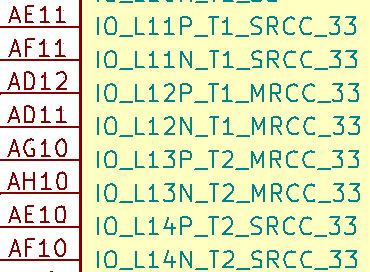

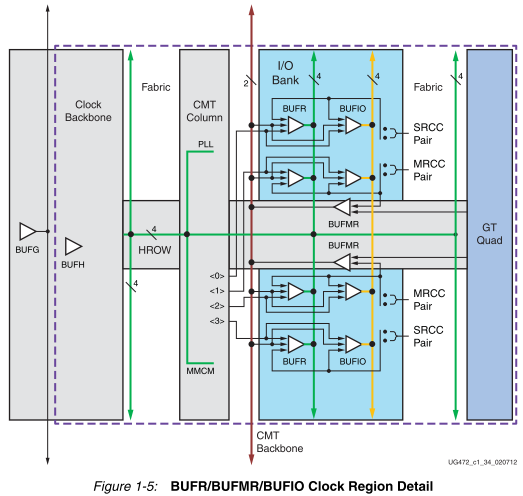

但是HR资源IO被完全占用,HP中只有bank33的MRCC/SRCC可以作为fpga的时钟输入。以及为了尽量减少差分晶振的数量,需要合理利用内部时钟资源。

一、先弄清楚DDR_controller的clk需求

调用MIG IP,选择DDR3 32位宽4GB。

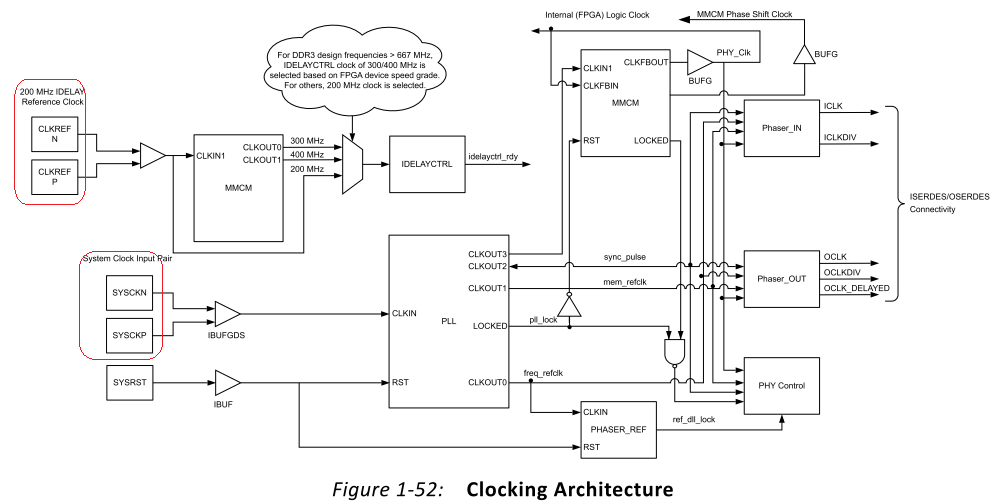

System Clock给DDR控制器逻辑和接口提供时钟;Reference Clock单独给Delay单元提供时钟,用来调整DDR信号时序。

Reference Clock:先来简单的,ref_clk给个固定的200MHz输入就可以了,可以认为跟ddr_controller这块是功能分开的。

You need to always supply a 200 MHz ref_clk and then MIG creates the appropriate IDELAYCTRL frequency with an additional MMCM.

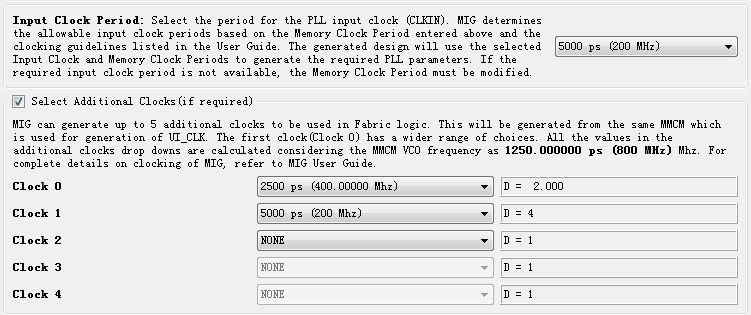

Input Clock Period:片子差分晶振频率,作为PLL模块的CLKIN。该PLL的VCO频率为800MHz(待确认)。

另外,这个模块能出5路 Additional Clock 给其他Fabric用,能否给user的logic?(待确认)

driven from an internal clock (No Buffer).

只有Input Clock Period是外挂200mhz时,Reference Clock才能选择Use System Clock。

建议两者都选 No Buffer,使用内部时钟。

Internal Vref 能释放 IO_0_VRN / IO_25_VRP 两个管脚,这里为什么不能勾选?(待确认)

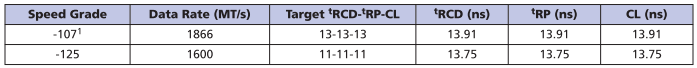

DDR颗粒选型:Micron MT41K1G8SN-107

二、内部时钟如何分配

7系内部分成了许多个clock region,每个region是50个CLB和IOB合集,且每个region内部有12个global clock domain,这些domain又能被级别最高的32个global clock buffer驱动。

而这些BUFG又能被CCIO直接驱动,即MRCC/SRCC时钟输入引脚。

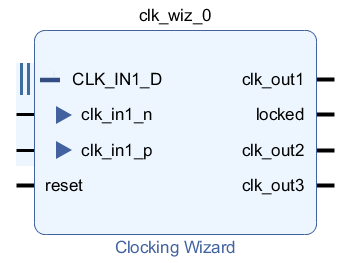

输入clk_in外接200Mhz晶振,经过clocking wizard输出三路时钟,分别给usr_clk、sys_clk、clk_ref

参考1:ug586_7Series_MIS

参考2:ug472_7Series_Clocking